Y2K compatible No-Slot-Clock for PC and XT - DS1216E Smartwatch

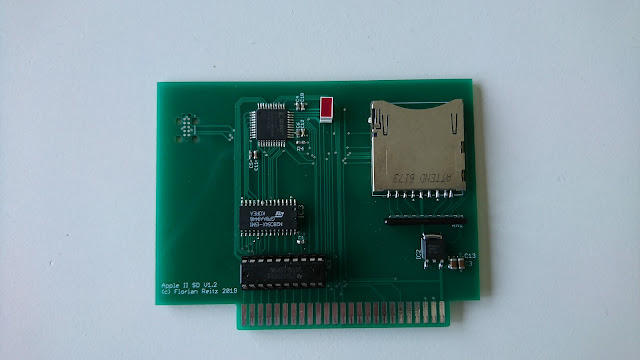

Last year around Christmas, I got hold of a Sanyo MBC-16 XT clone. The machine is nothing special, but it is the exact model my father had from the late 80s to the mid-90s and was most probably the first computer I sat in front of. Therefore, I couldn't resist when I saw one for sale. I will write about it in detail in an upcoming post. One of the upgrades I installed was a No-Slot-Clock based on a Dallas DS1216E Smartwatch chip. This is the same that also works in the Apple II series. In contrast to other RTCs, DOS doesn't know about this chip. You use it with a program from 1986 called SMWCLOCK.COM, originally provided by Dallas Semiconductor themselves (some sources say Tandy, but the assembly file says Dallas). Depending on the parameter, this program sets the time and date in the chip or reads from the chip and writes them to DOS. However, there is one problem with this program: It is not Y2K compatible, as most programs from this area. Nobody thought that it would be used...